Via Arrays

## Introduction

Many designs today require signals to be shielded. This can be on a net by net basis where the net is surrounded by an array of vias connected to a ground plane below, or the board profile may well have an array of grounding vias surrounding the complete profile to improve EMC performance. On a more general example, if the design is using multiple power and ground planes, designers require the ability to "stitch" the planes together using via arrays. Although some of these basic functions are available using an OrCAD PCB Designer Standard License (stitching vias) the other more advanced operations require the Allegro PCB Designer license.

## "Stitching" Vias.

To add stitching vias using an OrCAD PCB Designer Standard license use Route – Add Connect, go to the location for the first via and double click the LMB (left mouse button). This action adds a single via. It is important to note using this process to ensure that the actual via required is defined in Constraint Manager and that the active plane for connection (in this example GND) is the first layer visible. The net the via is connected to is the first plane found in the stackup so if you have a VCC plane on layer 2 the via added is connected to VCC. To alter this mode just display the layers you wish to connect from and that will be the default net used. There are many other ways to control this function and also please remember that this example is for a through via across all layers. Should your vias be defined as blind / buried you may need to define which via and layer you wish to connect from / to.

To create an array of stitching vias use the Edit – Copy command, once invoked look at the Options fold out menu for further settings:-

| 2 Options    | <b>џ ^</b>    |

|--------------|---------------|

| Copy mode:   | Rectangular 💌 |

| Qty          | Spacing Order |

| X: 10        | 35.0 Right -  |

| Y: 10        | 35.0 Down -   |

| Angle:       | 0.000 🗸       |

| Copy origin: | Symbol 🔻      |

| 📝 Retain r   | net of vias   |

You have options for a Rectangular or Polar Array, then Qty X and Y, spacing between vias and array direction and angle. For this example the copy options have been defined as shown. Please ensure that the Retain net of vias checkbox is checked, this ensures that any vias copied use the same net as the source via.

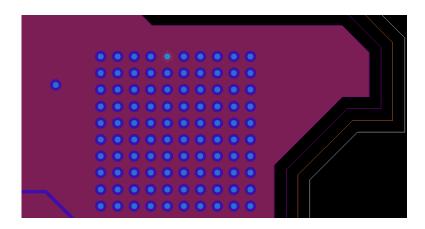

Once the settings are defined pick the source via and a new via is attached to the mouse, pick the location and the array of vias (in this case 100 vias) are added.

© 2015 Parallel Systems Limited

For users using an OrCAD PCB Designer Professional or an `Allegro PCB Designer license and above there is a menu command Place – Via Arrays – Matrix or Boundary. The Matrix option allows users to create via arrays. The Boundary option allows users to create via arrays that effectively follow a specific shape, area or net.

## Via Array - Matrix

To create a Matrix array use Place – Via Arrays – Matrix, then look at the options menu.

The Enable DRC check allows the tool to place vias based on the settings in the menu, then run a DRC check and any DRC errors that are produced the vias will automatically be deleted. The Operation Modes give the user the choice of the whole board, a specific area or a specific shape. If the area is selected users are prompted to select a start and finish location for the area. The via net option gives the user a choice to pick the net you wish to connect to, the padstack gives the user the option of which via to use (but only if you have multiple vias in the via list defined in Constraint Manager).

The remainder of the options are for distance to boundary plus horizontal and vertical via-via gaps. Finally the Thermal relief connects gives the user the option of how the via will connect to the plane.

As long as the Disable Preview button is not checked any settings that you apply will be shown on the screen. If you need to makes changes use RMB – Oops, then make the necessary changes, the display will be refreshed. If you are happy with the settings and via positions use RMB – Done, and the vias are confirmed.

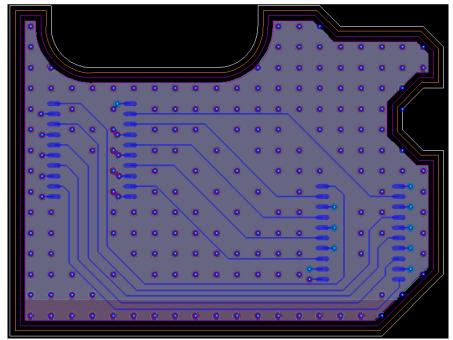

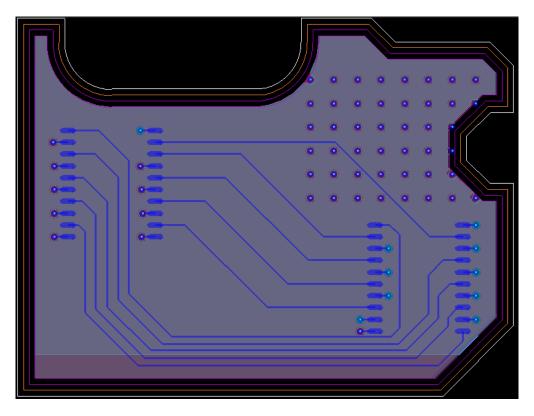

Below are examples of a Matrix array function.

Board Mode.

Area Mode

Shape Mode

## Via Array - Boundary

To create a Matrix array use Place – Via Arrays – Matrix, then look at the options menu.

| Options                                                                                                                                                                                                                                   | <b>₽</b>                                                               | * | × |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---|---|

| General options:<br>Enable DRC chr<br>Enable grouping                                                                                                                                                                                     |                                                                        |   |   |

| Via net and padsta<br>Via net:                                                                                                                                                                                                            | ck:                                                                    |   |   |

| Padstack:                                                                                                                                                                                                                                 | •                                                                      |   |   |

| Global ring paramet<br>Staggered rings<br>Inside shape/voids<br>Cline: On single sid<br>Number of rings:<br>Ring-ring spacing:<br>Object-ring parame<br>Non-circular obje<br>Circular object s<br>Via-object offset:<br>Maximum via-via g | ids<br>e of cline  I<br>I<br>ters<br>ect settings<br>ettings<br>I 00.0 |   |   |

| Thermal relief conn<br>Full contact                                                                                                                                                                                                       | ects                                                                   |   |   |

| Object-ring parame<br>Non-circular object s<br>Circular object s<br>Radius relative<br>Via array radius:<br>Via-via angle:<br>Start angle:                                                                                                | ect settings<br>ettings                                                |   |   |

The Enable DRC check allows the tool to place vias based on the settings in the menu, then run a DRC check and any DRC errors that are produced the vias will automatically be deleted. The enable grouping option allows users to merge the boundary shapes of all connected and overlapping objects and treat them as a single object while generating via arrays, along the single boundary shape.

The via net option gives the user a choice to pick the net you wish to connect to, the padstack gives the user the option of which via to use (but only if you have multiple vias in the via list defined in Constraint Manager).

The Global ring parameters define the following:-

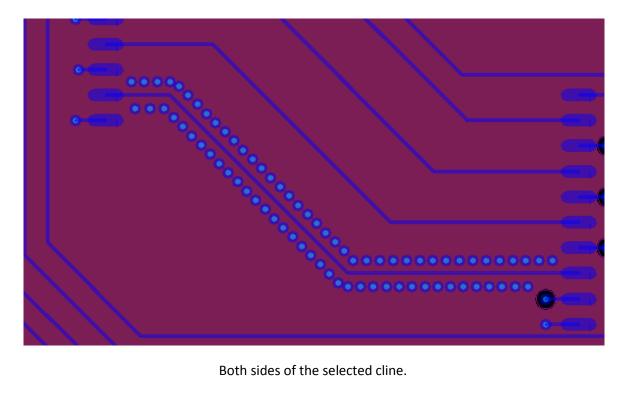

Inside shape/voids if checked will add vias inside the shape edge, if not checked they are placed on the outside of the selected shape. For the cline you have the choice of a single side or both sides of the selected cline or on the centre of the cline which adds vias which follow the cline itself. A diff pair is considered a single cline object. Number of rings specifies the number of rings for the via array. If the number of rings is more than one then the ringring spacing and staggered rings is enabled to give you further options for the type of via arrays that can be added.

Object-ring parameters are defined for Non circular objects:-

Via-object offset is the distance from the selected object to the first via and a maximum via-via gap distance.

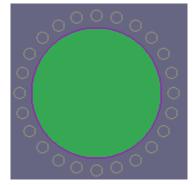

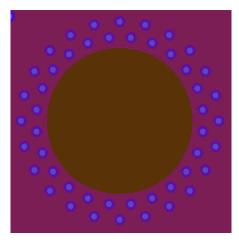

For Circular object settings:-

If the radius relative to boundary is set the via array radius value is the distance of the circle selected plus the via array radius. If not set it is the distance from the centre of the circle selected. For example if the via array radius is set to 25 and the radius relative to boundary is set then the array added is displayed as follows effectively offsetting the object selected by 25.

And if the radius relative to boundary is not checked effectively adding an array 25 mils from the centre point of the circle selected.

The via to via angle specifies the angle distance between vias and the start specifies the start angle location. Number of rings and ring to ring spacing define ring quantity and distance. The thermal relief connect specify how the via will be connected to the plane. The default is full contact.

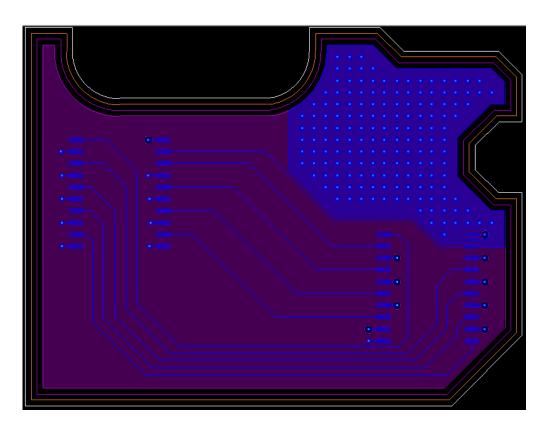

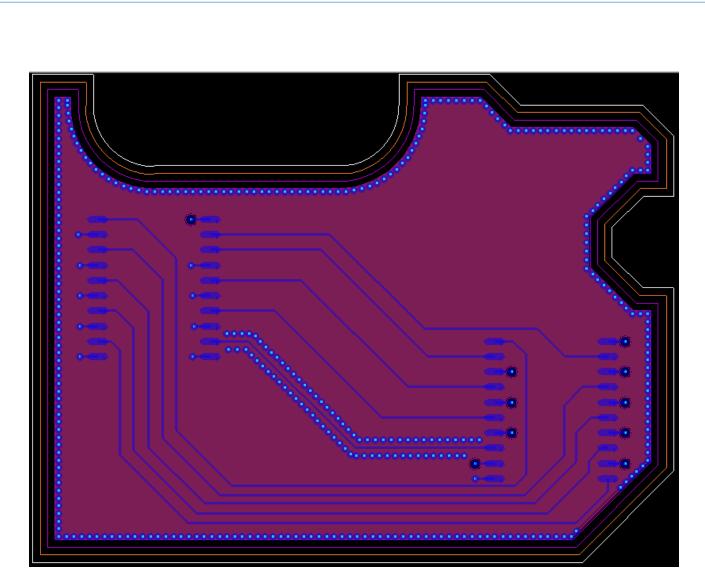

The following screenshots shows some examples of a boundary via array :-

Staggered – 2 rings

© 2015 Parallel Systems Limited

Board Edge selected

The following are trademarks or registered trademarks of Cadence Design Systems, Inc. 555 River Oaks Parkway, San Jose, CA 95134 Allegro<sup>®</sup>, Cadence<sup>®</sup>, Cadence<sup>®</sup>, Cadence logo<sup>™</sup>, Concept<sup>®</sup>, NC-Verilog<sup>®</sup>, OrCAD<sup>®</sup>, PSpice<sup>®</sup>, SPECCTRA<sup>®</sup>, Verilog<sup>®</sup> **Other Trademarks**

All other trademarks are the exclusive property of their prospective owners.

Via Arrays

**NOTICE OF DISCLAIMER:** Parallel Systems is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Parallel Systems makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Parallel Systems expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.