Matched Groups

## Introduction

You must be using OrCAD PCB Designer Professional or Allegro PCB Designer to use this function. A Match Group is a collection of nets, Xnets, or pin pairs which must all match (in time or length) or be relative to a specific target within the group.

# **Match Groups**

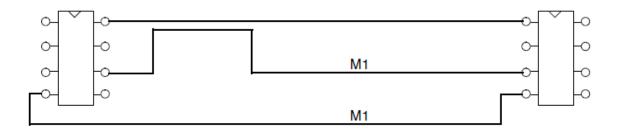

In this illustration two of the three nets belong to a Match Group - M1. To maintain a match propagation delay, you must extend the middle net to match the delay of the bottom net.

You can create Match Groups manually by adding properties directly to Xnets, or by using Constraint Manager to explicitly define pin pairs in an Electrical CSet. Regardless of the method that you choose, Match Groups are resolved down to specific pin pairs and are further defined by the following attributes: Scope, Delta, Tolerance and Target.

# Generating pin pairs for the Match Group members

Match Groups can be populated directly with pin pairs manually or through explicit pin pairs defined in an Electrical CSet. If the Match Group was instead created by adding nets or Xnets directly, an additional attribute is needed to guide the resolution of pin pairs that will ultimately be compared in the Match Group. In the Pin Pairs column of the Relative Propagation Delay worksheet, you can guide the generation of pin pairs with the following options:

| Choosing this option      | Generates pin pairs based on                                                                                 |

|---------------------------|--------------------------------------------------------------------------------------------------------------|

| All Drivers/All Receivers | All combinations of drivers and receivers.                                                                   |

| Longest Driver/Receiver   | The longest driver-receiver pin pair. Uses the Longest pin pair when there are not any drivers or receivers. |

| Longest Pin Pair          | The longest pin pair.                                                                                        |

When you analyze the Match Group, Constraint Manager automatically generates pin pairs based on the pinuse of the pins in the net or Xnet and the manhattan distances between the pins. Pin pairs appear hierarchically under the net or Xnet within the Match Group.

#### <u> Tip</u>

You create a Match Group in the Objects column of the Relative Propagation Delay worksheet by adding member nets and Xnets. If you cannot get the pin pairs that you want from the available settings, you should remove the net or Xnet from the Match Group, create the pin pairs that you want, and then add those pin pairs back to the Match Group.

# **Defining Match Group requirements**

The two main requirements for a Match Group are Delta and Tolerance, which occupy the Delta:Tolerance column in the Relative Propagation Delay worksheet. Based on these settings, a Match Group is further classified as Relative or Match.

# **Match Delay**

You specify only a Tolerance value; all pin pairs are compared against each other and must be within the specified Tolerance.

# **Relative Delay**

You specify both Delta and Tolerance values, and select a Target. The Target may be implicit or explicit; each pin pair is compared to the Target pin pair by the specified Delta and within the specified Tolerance.

The following attributes characterize the requirements for a Match Group:

- Tolerance Tolerance is the allowable skew when matching member pin pairs. You specify Tolerance as either length, delay, or a percentage. If you define only a Tolerance value for a member pin pair or for the Match Group, the member is compared to every other pin pair within the specified Tolerance. If you define a Delta value for a member, the member is matched to the Target, plus or minus the Delta and within the specified Tolerance.

- Delta Delta is the value added to, or subtracted from, the routed length of the Target. Delta determines the required length of the pin pair before applying the Tolerance. The Delta may be negative, in which case the value is subtracted from the routed length of the Target, or positive (or unsigned), in which case the value is added to the routed length of the Target. You can specify Delta as either length or delay. If the Delta is unspecified, the pin pair must match all other pin pairs in the Match Group (within the Tolerance). A design rule violation results when the difference is greater than the Tolerance.

**Note:** If you specify zero for a Delta (which is different from leaving the field blank), the value is compared directly to the routed length or delay of the Target.

Target is a pin pair that is referenced by all pin pairs in the Match Group. Target applies only When a Delta value exists; only one Target is specified for the entire Match Group. When you explicitly set the Target pin pair (using the right mouse button), it remains the Target. When the Target is not user defined, it may change from one net to another based on changes to the original Target, such as a change in its manhattan length. If a pin pair is the Target in one Match Group, it does not have to be the Target in another Match Group, if that pin is a member of multiple Match Groups.

# **Determining the target pin pair**

In a Match Group, Constraint Manager selects one of the pin pairs (or you specify one) as the Target and all of the other pin pairs are matched against this Target within the given Delta and Tolerance. When you manually specify a Target, there are no Delta and Tolerance values for that row. If the TARGET keyword is displayed in the Delta/Tolerance cell for more than one member of a Match Group, the constraint information is invalid. You should clear or enter an explicit delta/tolerance value for each member that should not be considered the Target.

Constraint Manager determines the Target pin pair as follows. The pin pair . . .

- **1.** That you explicitly set (using the right mouse button in the Delta:Tolerance column).

- 2. With the smallest absolute Delta value (if all pin pairs have a Delta value).

- 3. With the longest manhattan length (if more than one pin pair has the same smallest Delta value).

**Note:** If none of the pin pairs has a Delta value, no Target is chosen; therefore, all pin pairs are compared to each other and the group is considered match delay, not relative match delay.

For example, if one pin pair has a Delta value of -300 and two pin pairs have a Delta value of zero, the pin pair with a zero Delta and the longest manhattan distance is chosen as the default Target. Although zero is larger than -300, the absolute value of -300 is 300, which is larger than zero. The two pin pairs with the zero value are compared by manhattan distance, and the larger is selected as the Target.

Note: When the Delta for all pin pairs is set to Null, the delay is considered match delay, not relative match delay.

#### Scope

Scope controls the validation of the Match Group (Local and Global), as well as the generation of Match Groups (Bus and Class). Once you define the members of a Match Group, you can specify the scope in the:

- Scope column of the Relative Propagation Delay worksheet (in the Net folder).

- Scope column of the Relative Propagation Delay worksheet (in the Electrical Cset folder).

- Relative Prop Delay tab in SigXplorer (choose Set Constraints).

You can specify the following scope options:

- Local Validates only pin pairs within each net (or Xnet) against other pin pairs in the same net (or Xnet) for each member of the Match Group.

- Global Validates all pin pairs against all other pin pairs in the Match Group.

Bus Bus scope is useful in situations where groups of signals are replicated and constraining them would require multiple Electrical CSets that only differ by Match Group name. If the nets that reference the Electrical Cset are not grouped into buses, a single Match Group with a Global scope is created.

**Note:** Bus scope can only be set in an Electrical CSet and only applies during the Electrical CSet mapping process. If you subsequently apply the Electrical CSet to:

- A bus member, Constraint Manager maps the Match Group constraints to the bus member.

- The parent Bus object, Constraint Manager maps the Match Group constraints to all members of the Bus.

- A non-Bus member, Constraint Manager applies a Global scope and retains the original name of the Match Group.

When an Electrical CSet is applied to nets, all generated pin pairs are added to unique Match Groups based upon their Bus membership. The unique Match Group name is based upon the Electrical CSet Match Group name suffixed with the Bus name. The generated Match Group is created with a scope of Global so that they are validated appropriately, as defined above in the Global setting. The Bus scope setting allows you to reference the same Electrical CSet from multiple Buses, resulting in unique Match Groups for the members/pin-pairs of each Bus (as required). This reduces the number of ECSets needed to constrain a design.

Class

Class scope is useful in situations where groups of signals are replicated and constraining them would require multiple Electrical CSets that only differ by Match Group name. If the nets that reference the Electrical Cset are not grouped into Classes, a single Match Group with a Global scope is created.

**Note:** You can set Class scope only in an Electrical CSet and it only applies during the Electrical CSet mapping process.

When an Electrical CSet is applied to nets, all generated pin pairs are added to unique Match Groups based upon their Class membership. The unique Match Group name is based upon the Electrical CSet Match Group name suffixed with the Class name. The generated Match Group is created with a scope of Global so that they are validated appropriately, as defined above in the Global setting. The Class scope setting allows you to reference the same Electrical CSet from multiple Classes, resulting in unique Match Groups for the members / pin-pairs of each Class (as required). This reduces the number of ECSets needed to constrain a design.

Class scope is more flexible than Bus scope because a Class can include more disparate signals than a Bus can. A Bus is typically limited to vectored nets or nets that share a common topology; a Class often includes control signals, too.

You can also use Class and Bus scope to ensure that unique Match Groups are created in the top level of a hierarchical design in Allegro Design Entry HDL or Allegro System Architect, where replicated blocks exist.

**Important** The default configuration for Electrical Classes is Local, which allows for electrical constraints and Match Groups to be created in a hierarchical block, and remain specific to that block at a higher level, and also in PCB Editor.

# **Match Group Rules**

The following rules apply to Match Groups:

- You must specify a Match Group in only the Relative Propagation Delay worksheet of the Routing workbook.

- You can set Match Group constraints for the entire group and override individual members of the group as desired, offering differing levels of delta and tolerance.

- You specify Match Group delays at the design or the system-level.

- You can include a Match Group member in multiple Match Groups.

- A match delay constraint from a pre-14.0 board database is upreved with a delta value of zero. This implies that all group members will match a specified target pin pair.

**Note:** Constraint Manager, when launched from Allegro<sup>®</sup> PCB Series L, supports Match Groups only on netrelated objects, not on Electrical CSets.

• If you are specifying a Bus or Class-scope, you must create the Match Group in a CSet in the Electrical CSet folder.

### **Multi-group Membership**

You can include a member of a Match Group in another Match Group. In this way, you can constrain the same member differently in each Match Group. In the figure below, members CASOL and CAS1L are members of two Match Groups. Furthermore, CAS1L is constrained differently in each Match Group.

| 🖌 design         |                           |  |        | -           |

|------------------|---------------------------|--|--------|-------------|

| MATCH_GROUP_B(4) | All Drivers/All Receivers |  | Global | 100 ns:5 %  |

| BHEL             | All Drivers/All Receivers |  | Global | 100 ns:5 %  |

| BLEL             | All Drivers/All Receivers |  | Global | 100 ns:5 %  |

| CASOL            | All Drivers/All Receivers |  | Global | 100 ns:5 %  |

| CAS1L            | All Drivers/All Receivers |  | Global | 100 ns:5 %  |

| MATCH_GROUP_C(8) | All Drivers/All Receivers |  | Global | 100 ns:5 %  |

| CASOL            | All Drivers/All Receivers |  | Global | 100 ns:5 %  |

| CAS1L            | All Drivers/All Receivers |  | Global | 150 ns:10 % |

**Note:** Refer to the Objects > Create > Match Group and Objects > Group Members commands in the Constraint Manager Reference for information on including nets, Xnets, and pin pairs in multiple Match Groups.

Analyzed values appear in the Actual and Margin columns of a net, Xnet, or pin pair. If you include the net, Xnet, or pin pair in a Match Group, the analyzed values appear on that member in each Match Group to which it belongs, and not on the object's row outside of the Match Groups. To obtain the value of a net, Xnet, or pin pair that is a Match Group member, you must expand that Match Group.

With multi-group membership, use the following techniques to locate Match Group member objects:

• Status Bar Highlight a net, Xnet, or pin pair in the Object's column and observe the status bar. Constraint Manager reports all parent objects in which the member belongs.

PinPair Result: J1A.1:J1B.1 [Match Group MG1, Net BANKJ1\_1OF50]

In the example above, the status bar (located at the lower-left corner of Constraint Manager) identifies the pin pair, its parent net, and the parent Match Groups.

#### Matched Groups

- Find Use the Find command (choose Edit Find) to locate the selected object. Use the Find Next command (choose Edit Find Next) to find the next occurrence of the object in your design. One at a time, Constraint Manager locates the next occurrence of the selected object in all parent objects to which it belongs, including multiple Match Groups.

- Select Use the Select command to highlight all occurrences of the selected object, including instances of the object in multiple Match Groups.

- Filter Use the Filter command (choose Objects Filter) to locate only the occurrences of a selected net or Xnet, including instances of the object in multiple Match Groups. Where Select locates an instance of an object in multiple groups, Filter lets you filter out members of the Match Group.

#### **Summary**

After creating a new matched group, you need to set the constraint values for the matched group. You can set the Pin Pairs constraint to one of three different values. **Longest Pin Pair** will verify that the longest pin pair on each of the nets in the matched group is within the delta and tolerance specified. **Longest Driver/Receiver** will verify that the longest driver and receiver pair on each net is within the delta and tolerance specified. **All Drivers/All Receivers** will verify that every driver and receiver pair is matched within the delta and tolerance specified. You set Scope constraint to either **Global** or **Local**, which controls how the members of the group are validated against the delta and tolerance. When set to Local, the driver and receiver pairs are only validated against driver and receiver pairs on the same net or Xnet. The Local setting only makes sense when the Pin Pairs constraint is set to All Drivers/All Receivers. When the Scope is set to **Global**, the specified pin pairs are being validated across all the nets defined in the matched group. The **Delta:Tolerance** constraint specifies the allowable propagation delay or length delta and tolerance for the pin pairs of the group. The delta is used to offset the Pin Pair(s) from a target Pin Pair. The delta can be specified in either absolute length or delay (License dependant). The tolerance is used exclusively for match delay and can also be used in conjunction with the delta value for relative delay. The tolerance relaxes the relative/match requirements. The tolerance can be specified in either absolute length/delay or as a percentage of length or delay (License dependent).

The following are trademarks or registered trademarks of Cadence Design Systems, Inc. 555 River Oaks Parkway, San Jose, CA 95134 Allegro<sup>®</sup>, Cadence<sup>®</sup>, Cadence<sup>®</sup>, Cadence logo<sup>™</sup>, Concept<sup>®</sup>, NC-Verilog<sup>®</sup>, OrCAD<sup>®</sup>, PSpice<sup>®</sup>, SPECCTRA<sup>®</sup>, Verilog<sup>®</sup> **Other Trademarks**

All other trademarks are the exclusive property of their prospective owners.

**NOTICE OF DISCLAIMER:** Parallel Systems is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Parallel Systems makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Parallel Systems expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.