## How to Define a Double Sided Surface Mount Component

## Introduction

There are many requirements for PCB design today that need an edge connector that has connections on both sides of the PCB. Because of the way surface mount pads are defined in PCB Editor (TOP side by default) you need to define a different padstack for both TOP and BOTTOM sides of the PCB so you can create a double sided surface mount part.

## How to Define a Double Sided Surface Mount Component.

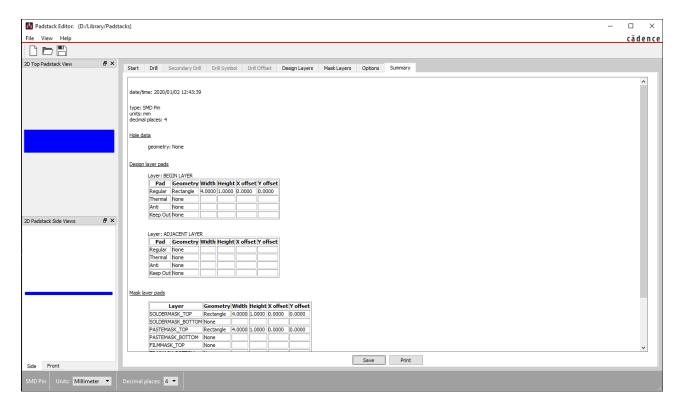

To define this type of component (normally an edge connector with alternate pins on the Top and Bottom side of the PCB) we need to define two pad types. Using Padstack Editor the first would be defined as a SMD PIn type pad as shown below.

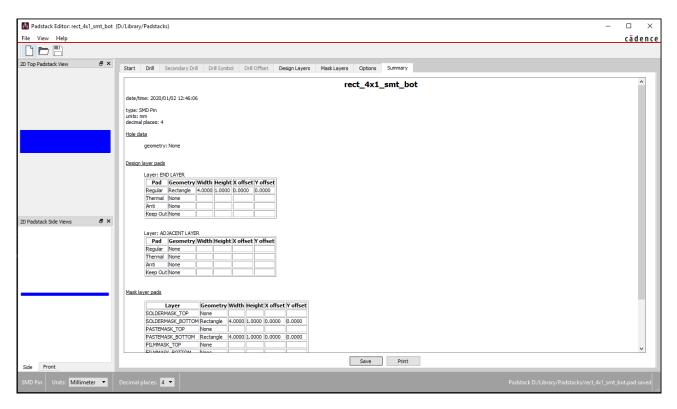

For the bottom version create a new Pad (I used a similar name as the first so rect\_4x1\_smt but for the bottom side added \_bot to the name). Go to the Design Layers tab and change the BEGIN LAYER drop down and change it to END LAYER.

Change the SOLDERMASK\_TOP and PASTEMASK\_TOP definitions to use SOLDERMASK\_BOTTOM and PASTEMASK\_BOTTOM on the Mask Layers tab then save as the new name.

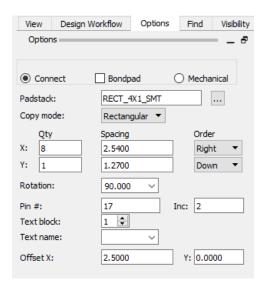

Start PCB Editor and create a new package symbol (connector.dra). Add the first set of pins, use the options box to add only odd numbered pins (Change the Inc to 2).

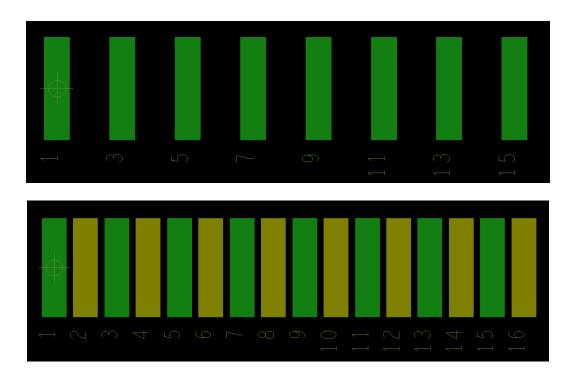

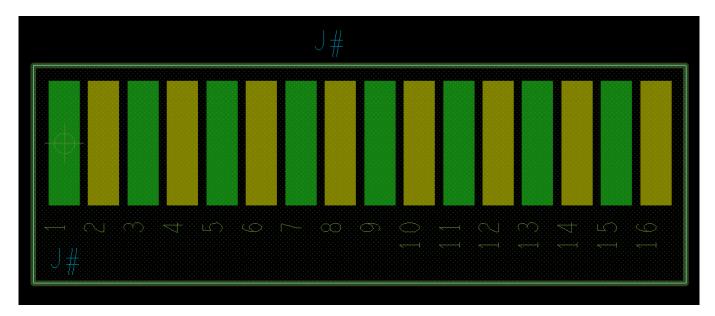

So that you have pins numbered 1, 3, 5, 7, 9, 11, 13, and 15. See below left. Then add the bottom defined pad (change the start to be 2) and add pin 2, 4, 6, 8, 10, 12, 14, 16. See below right. For this example, Pads are shown in different locations for clarity. In reality the TOP and BOTTOM pads would be on at the same x, y locations.

You can now add silkscreen, assembly, placement areas and text to complete your pcb footprint design.

Your completed pcb footprint should look similar to the example below. When you add this part to a board design you will only have surface mount style pads and the pins will alternate the top and bottom layers as shown.

The following are trademarks or registered trademarks of Cadence Design Systems, Inc. 555 River Oaks Parkway, San Jose, CA 95134 Allegro®, Cadence®, Cadence logo™, Concept®, NC-Verilog®, OrCAD®, PSpice®, SPECCTRA®, Verilog®

## Other Trademarks

All other trademarks are the exclusive property of their prospective owners.

**NOTICE OF DISCLAIMER:** Parallel Systems is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Parallel Systems makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Parallel Systems expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.