# The Capture Constraint System

# **The Capture Constraint System**

The Capture Constraint System, provides access to the Constraint Manager to allow management of rules for a PCB Editor design from OrCAD Capture.

The purpose of this note is to provide an overview of the Capture Constraint System and not provide a detailed discussion of the application of the constraints. A detailed discussion is covered in the Constraint Manager Reference Guide available from the Cadence Help application in HTML form, or available for download from the Cadence Online Support site.

Since the schematic "knows nothing" about the physical PCB being designed, access to rules which rely on knowledge of the board cross section will not be available unless a template board, or a technology file, is loaded. Users may create their own templates and technology files, with any of the OrCAD, or Allegro, PCB Editor tools. Users of standalone OrCAD Capture can create a default board to use as a template, this is discussed in more detail later in this note.

# What rules are available

Rules shown in the Capture Constraint System reflect the license that OrCAD Capture was started from. With an OrCAD Capture, or an OrCAD PCB Designer Standard license, only rules applicable to the OrCAD PCB Designer Standard will be available. Rules applicable to OrCAD PCB Designer Professional will be available if an OrCAD Capture CIS, or OrCAD PCB Designer Professional license is used.

# **Enabling the Constraint Manager flow**

When OrCAD Capture, or OrCAD Capture CIS starts, the Constraint Manager icon will be displayed in the toolbar.

To enable the Constraint Manager flow, left-click the Constraint Manager icon.

| Enable Constraint Manager                                                                                 |  |

|-----------------------------------------------------------------------------------------------------------|--|

| To setup and manage constraints in your design:                                                           |  |

| 1. Complete logical design                                                                                |  |

| 2. Add electrical constraints in Constraint Manager                                                       |  |

| 3. Create or synchronize the PCB layout                                                                   |  |

| 4. Update electrical, physical, and spacing constraints in PCB layout                                     |  |

| 5. Run Design Sync to synchronize constraints                                                             |  |

| Notes:                                                                                                    |  |

| - Specify the Voltage property for power nets.                                                            |  |

| - Import technology file in Constraint Manager to add physical and spacing constraints in logical design. |  |

| For details about the Capture - Constraint Manager flow, click Help                                       |  |

| Do not show this message again OK Help                                                                    |  |

### Left-click>OK

The Migrate Constraints form will be shown.

## For designs without PCB layout

If there is no PCB, leave the "Migrate Constraints from Schematic Design" set and specify the Units and accuracy, "mm" and 2 decimal places would be typical.

| Migrate Constraints                                                                                                                                                                                                      |                                           |                                       | × |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------|---|

| Select the option to migrate design constraints from schematic o                                                                                                                                                         | r PCB layout to Constra                   | aint Manager.                         |   |

| <ul> <li>Migrate constraints from schematic design<br/>(For designs without PCB layout)</li> <li>Migrate constraints from PCB layout<br/>(For designs with constraints in PCB layout)</li> <li>Do not migrate</li> </ul> | Select the constrain<br>Units<br>Accuracy | ts unit and accuracy (decimal places) |   |

|                                                                                                                                                                                                                          |                                           | ОК Неір                               |   |

Left-click>OK to convert the project to "Constraint Manager Enabled". (Refer to Note 1 page 7).

Then the Assign Voltage Nets to Power Nets form will open.

| Assign Voltage to Power Nets                       |            | >                    |

|----------------------------------------------------|------------|----------------------|

| Specify voltage for power and g                    | round nets |                      |

| Power Nets                                         |            | tage                 |

| VSS                                                | 0.0        |                      |

| VREFCA                                             | 1.5        | V                    |

| VSSQ                                               | 0.0        | V                    |

| VDDQ                                               | 1.5        |                      |

| VREFDQ                                             | 1.5        |                      |

| VDD                                                | 1.5        | V                    |

| Auto-assign voltage values Specify default voltage |            | nt designs           |

| Ground Nets                                        |            | 0.0V                 |

| Power Nets                                         |            | 1.5V                 |

| Naming convention to<br>ground nets                | identify   | *GND*,*GROUND*,*VSS* |

| ОК                                                 | Cance      | l Help               |

|                                                    |            |                      |

Assign appropriate voltages to the Voltage Nets. (Use the Auto Assign settings to automatically assign Voltages to Power Nets in other designs opened and Constraint Manager enabled in the same Capture session)

(The Assign Voltage Nets to Power Nets form can also be opened from the SI Analysis>Identify DC Nets menu)

#### Left-click>OK

(A report is generated that shows the list of transferred constraints, constraint properties (if any), and warnings (if any). To review the report summary, use the Window>Session Log menu)

#### The Constraint Manager window opens.

| 🎢 Constraint Manager (connected to CAPT | TURE) [TEST1] |       |       |    |       |         |      |            |      |         | _                     |          | ×   |

|-----------------------------------------|---------------|-------|-------|----|-------|---------|------|------------|------|---------|-----------------------|----------|-----|

| File View Audit Tools Help              |               |       |       |    |       |         |      |            |      |         |                       |          |     |

| 8 % C C 4                               |               | 10 73 | 7. 7. | 市電 | 76 76 | <br>- = | -    | <b>G</b> A | #    | ŏ 🗿     | )<br>m<br>B<br>m<br>+ |          |     |

|                                         | ₽×            |       |       |    |       |         |      |            |      |         |                       |          |     |

| 🗳 Electrical                            |               |       |       |    |       |         |      |            |      |         |                       |          |     |

| 🕆 🗎 Electrical Constraint Set           |               |       |       |    |       |         |      |            |      |         |                       |          |     |

| > 🕅 Routing                             |               |       |       |    |       |         |      |            |      |         |                       |          |     |

| ✓ ► Net<br>> ■ Routing                  |               |       |       |    |       |         |      |            |      |         |                       |          |     |

| +/+ Physical                            |               |       |       |    |       |         |      |            |      |         |                       |          |     |

| Spacing                                 |               |       |       |    |       |         |      |            |      |         |                       |          |     |

| 🖾 Same Net Spacing                      |               |       |       |    |       |         |      |            |      |         |                       |          |     |

| Properties                              |               |       |       |    |       |         |      |            |      |         |                       |          |     |

| Design Instance/Block filter            | ₽×            |       |       |    |       |         |      |            |      |         |                       |          |     |

|                                         |               |       |       |    |       |         |      |            |      |         |                       |          |     |

|                                         |               |       |       |    |       |         |      |            |      |         |                       |          |     |

|                                         |               |       |       |    |       |         |      |            |      |         |                       |          |     |

|                                         |               |       |       |    |       |         |      |            |      |         |                       |          |     |

|                                         |               |       |       |    |       |         |      |            |      |         |                       |          |     |

|                                         |               |       |       |    |       |         |      |            |      |         |                       |          |     |

|                                         |               |       |       |    |       |         |      |            |      | Sum a - |                       |          | - 4 |

|                                         |               |       |       |    |       | <br>    | ldle |            | <br> | Sync o  | n.    t               | FLTR_PAN |     |

### For designs with constraints in PCB layout

Select the "Migrate Constraints from PCB layout" option.

| Migrate Constraints                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                            | × |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Select the option to migrate design constraints from schematic or                                                                                                                                                        | r PCB layout to Constraint Manager.                                                                                                                                                                                                                                                                        |   |

| <ul> <li>Migrate constraints from schematic design<br/>(For designs without PCB layout)</li> <li>Migrate constraints from PCB layout<br/>(For designs with constraints in PCB layout)</li> <li>Do not migrate</li> </ul> | To complete the constraints migration you are required to perform following design<br>synchronization steps.<br>1) Run Update Layout to synchronize schematic to layout.<br>2) Run Update Schematic to synchronize layout to schematic.<br>3) Open Constraint Manager to view, edit or update constraints. |   |

|                                                                                                                                                                                                                          | OK Help                                                                                                                                                                                                                                                                                                    |   |

| Left-click>OK and the steps from the form MUST                                                                                                                                                                           | be then performed, in order, to complete the Constraint                                                                                                                                                                                                                                                    |   |

Manager enabled flow migration:

- 1) Use PCB>Update Layout and synchronise the current schematic onto the board file. (the board does not need to be opened)

- 2) Use PCB>Update Schematic and synchronise the board file back to the schematic (including Constraints).

- 3) Use the Constraint Manager to View, Edit or Update the Constraints.

(Note that only changes are transferred by this processing, so any existing board assigned Constraints will not be changed, since the Schematic has none until the migration processing has been completed)

## **Getting Physical and Spacing Constraints without a PCB**

#### If you have a Capture license and no technology, file

You can create a BRD file by running the Design Sync command into a "default" board file without opening the board file, then running Design Sync again from that BRD file back to the schematic. To do this run PCB>Design Sync Setup and change the Select Layout Tool from PCB Editor to Update Layout and Do Not Open.

| Design Sync Setup                   | ×                               |

|-------------------------------------|---------------------------------|

| ✓ Layout Tool and Design Sync Optic | ons                             |

| Layout Folder                       | allegro                         |

| Allow Etch Removal                  | No 💌                            |

| Create User Defined Properties      | No 👻                            |

| Select Layout Tool                  | Update Layout and Do Not Open 👻 |

| ✓ Placement                         |                                 |

| Place Change Component              | Always 👻                        |

| Ignore Fixed Property               | No 👻                            |

| ✓ Constraints                       |                                 |

| Constraints                         | Changes Only -                  |

| Show Difference Report              | Yes 👻                           |

| V PCB Netlist                       |                                 |

| Configuration file                  | C:\Cadence\SPB 17.4             |

| comparation me                      | C:\Cadence\SPB_17.4             |

|                                     | Ok Cancel Help                  |

Choose OK and then run PCB>New Layout

| New Layout                             |                   | × |

|----------------------------------------|-------------------|---|

| Create New Layout and Associate in Pro | oject             |   |

| PCB Layout Folder                      | allegro           |   |

| Input Board File                       |                   |   |

| Board                                  | allegro\test3.brd |   |

|                                        |                   |   |

|                                        | Ok Cancel Help    |   |

Leave the defaults and click OK. You will notice the board file is created and shown in the Project window under the Layout section. Now choose PCB>Update Schematic and left-click>Sync.

| 🔳 Updat           | e Schematic                                                  | ×   |

|-------------------|--------------------------------------------------------------|-----|

| Schematic         | C:\ORCAD_TRAINING\CAPTURE\CMLABS\EXAMPLE1\RELEASE.opj        |     |

| Layout            | :\ORCAD_TRAINING\CAPTURE\CMLABS\EXAMPLE1\allegro\release.brd |     |

| Info<br>There are | e no connectivity differences to show.                       |     |

| \$                | Sync Can                                                     | cel |

You can then use the Constraint Manager to View, Edit or Update the Constraints. (Note: PCB Footprints MUST be available for this to work successfully).

You can load a technology file by launching the Constraint Manager from within Capture and using the File>Import>Technology file entry, browse to the technology file and use the Overwrite option to load all the constraints from the technology file.

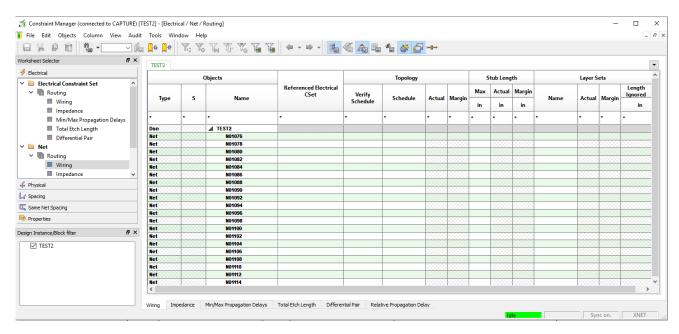

### **The Constraint Manager window**

The Constraint Manager has the Worksheet Selector at the left-hand side to allow the Worksheet to be selected from the Domain of interest. Domains are: Electrical, Physical, Spacing, Same Net Spacing and Properties. Note that, at this point, the Physical, Spacing and Same Net Spacing are not enabled, unless the design has been synchronised with a Board file.

Within the Domains are Workbooks and Worksheets which is where the values for the rules are entered. The following screenshot shows the Electrical>Electrical Constraint Set>Routing Workbook selected, and the Wiring Worksheet opened. Note that other Worksheets can be selected from within this Workbook by selecting the tabs at the bottom. The Electrical Constraint Set values are set in this Worksheet and then applied to Nets and Net Classes in the Electrical>Net>Routing>Wiring Worksheet.

| <ul> <li>Constraint Manager (connected to CAPTURE) [Times File Edit Objects Column View Audit</li> </ul>                                                                                |             |          |                            | a]                |                 |        |             |            | -        | ×          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|----------------------------|-------------------|-----------------|--------|-------------|------------|----------|------------|

|                                                                                                                                                                                         |             | Yo Yo    |                            | ⊊ ( + + ⇒         | -               | A 🖡 4  | ta 😽 🗗 🕶    |            |          |            |

| Worksheet Selector & X                                                                                                                                                                  | TEST2       |          |                            |                   |                 |        |             |            |          | •          |

| 🖗 Electrical                                                                                                                                                                            |             | 0        | bjects                     | To                | pology          | Stub   | Max Exposed |            |          |            |

| Electrical Constraint Set     Routing                                                                                                                                                   | Туре        | s        | Name                       | Verify            | Schedule        | Length | Length      | Layer Sets |          |            |

| Wiring Impedance                                                                                                                                                                        |             |          |                            | Schedule          |                 | in     | in          |            |          |            |

| Min/Max Propagation Delays                                                                                                                                                              | ŀ           | •        | •                          | •                 | •               | •      | •           | •          |          |            |

| III Total Etch Length                                                                                                                                                                   | Dsn         |          | TEST2                      |                   |                 |        |             |            |          |            |

| III Differential Pair                                                                                                                                                                   |             |          |                            |                   |                 |        |             |            |          |            |

| <ul> <li>Net</li> <li>Routing</li> <li>Wring</li> <li>Impedance</li> <li>Imredance</li> <li>Total Etch Length</li> <li>Differential Pair</li> <li>Relative Propagation Delay</li> </ul> |             |          |                            |                   |                 |        |             |            |          |            |

| +(+ Physical                                                                                                                                                                            |             |          |                            |                   |                 |        |             |            |          |            |

| , Y Spacing                                                                                                                                                                             |             |          |                            |                   |                 |        |             |            |          |            |

| 🔣 Same Net Spacing                                                                                                                                                                      |             |          |                            |                   |                 |        |             |            |          |            |

| 🎭 Properties                                                                                                                                                                            |             |          |                            |                   |                 |        |             |            |          |            |

| Design Instance/Block filter 🗗 🗙                                                                                                                                                        |             |          |                            |                   |                 |        |             |            |          |            |

| Ø TEST2                                                                                                                                                                                 |             |          |                            |                   |                 |        |             |            |          |            |

|                                                                                                                                                                                         | L           |          |                            | 1                 |                 |        |             |            |          |            |

| Routing layer sets (LAVERSET_GROUP)                                                                                                                                                     | Wiring Impe | edance I | Min/Max Propagation Delays | Total Etch Length | Differential Pa | ir     |             | ldie       | Sync on. | FLTR_PANE4 |

There are more columns in the Electrical>Net>Routing>Wiring Worksheet because the Net Worksheets will show the Actual values for the routing and Margins between the routed Nets and the Constraints set for them.

## **The Constraint Domains**

The Physical domain sets the rules for the routing for the design. The routed width, via selection, differential pair coupling parameters, blind and buried via stagger, "T"s and routing on layers.

The Spacing domain sets the rules for spacing between net objects in the design where nets are different. Line routed lines, vias, pins and so on. There are many settings since each object to object combination must be catered for.

The Same Net Spacing sets the rules for spacing between net objects where nets are the same.

The Electrical domain sets the rules for high speed designs where the routing needs to be controlled, or matched to ensure integrity of signal timing, for example.

The Properties domain will list properties for nets and components. The Voltage property that is set at the constraint manager launch is one example.

## **Creating Constraint Sets**

Constraint Sets can be created in the Electrical, Spacing or Same Net Spacing Domains. Left-click in the Domain, then the Constraint Set type. For the Electrical Constraint Set, left-click in the Design Name entry and rightclick>Create Electrical CSet. For the Physical, Spacing and Same Net Spacing Constraint Sets, left-click in an existing Constraint Set, Default for example, and right-click>Create Physical CSet, Spacing CSet, or Same Net Spacing CSet, depending upon which domain is active. Once the new Constraint Set is added, set the values.

### **Applying constraints**

Typically, rules are set within a Constraint Set for the domain, Nets that require the same Constraint Set are grouped into Net Classes and then the required Constraint Set is applied to the Net Class. If required, Constraint Sets can be applied to individual Nets and values can also be applied to individual Nets using the cells for the values.

Constraints can be applied through the Constraint Manager in Capture, the design synced through to PCB Editor, modified in PCB Editor and then design synced back to Capture, keeping the schematic and the board tightly coupled.

# XNet automated creation

Once the Constraint Manager flow is enabled, XNets, eXtended Nets where a "terminator" combines two Nets, will be automatically created for any two pin components with a CLASS Property Value of DISCRETE, effectively assuming that they are "coupling" individual Nets into an eXtended Net. To avoid the creation of eXtended Nets where not intended, two pin components with a CLASS Property Value of DISCRETE will require the "NO\_XNET\_CONNECTION" Property with a Value of YES to be applied to the Part.

Note that only numerical values are recognised for the Value property to correctly create XNets. If the Value property isn't numerical, for example the Value is "22R 1%", the XNET\_PINS property will be required on the Pins of the part to create the XNet, use the same value of XNET\_PINS assigned to the pair of Pins to create the XNet. Using a two-pin resistor as an example, the XNET\_PINS property would be assigned to both Pins with the same value on each of them.

# **Notes:**

- Back up your design before enabling Constraint Manager because once enabled, you cannot change it to a non-Constraint Manager-enabled design. (A copy of the DSN file is saved as <design\_name>.dsn.3sav when the Capture Constraint Manager is invoked)

- 2) As far as practicable, modify the constraints after completing the design.

- 3) Specify the Voltage property for power nets.

- 4) Import the technology file in Constraint Manager to add physical and spacing constraints in the logical design.

- 5) For distributed design environment, manage constraints in a single environment. It is recommended that constraints are added either in Capture or in PCB layout before running the schematic to PCB and PCB to schematic flows.

- 6) If a board is associated with a design, to migrate constraints, ensure that you use the Import from physical layout option in the Migrate Constraints dialog box.

- 7) Do not rename a Constraint Manager-enabled non-root-schematic design, else the all the constraints will be lost.

- 8) If the Constraint Manager-enabled design is opened in a lower release version of Capture and edited, the constraints will be lost.

The following are trademarks or registered trademarks of Cadence Design Systems, Inc. 555 River Oaks Parkway, San Jose, CA 95134 Allegro®, Cadence®, Cadence logo™, Concept®, NC-Verilog®, OrCAD®, PSpice®, SPECCTRA®, Verilog®

Other Trademarks

All other trademarks are the exclusive property of their prospective owners.

NOTICE OF DISCLAIMER: Parallel Systems is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Parallel Systems makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Parallel Systems expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.