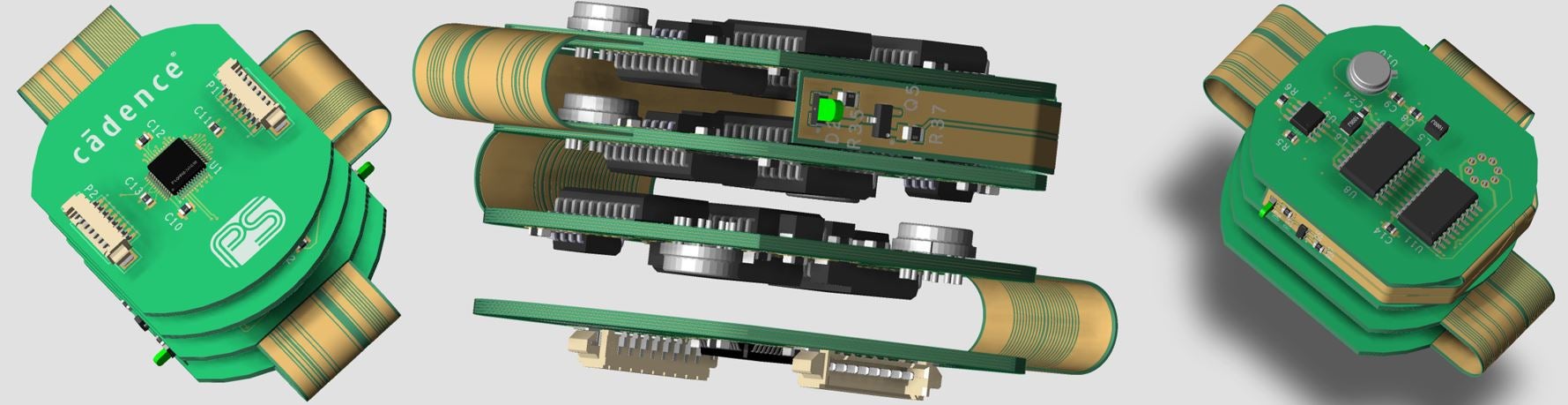

“With Allegro TimingVision, the routing process has sped up dramatically, from four weeks, down to four days,”

Bill Munroe - Cavium

Designed with Cadence.

Download design files here...

“We’re very optimistic about our future with the scalable OrCAD PSpice and Allegro PCB Designer tools"

The Cadence solution reduces our PCB development time by 80 percent

- Gisbert Thomke, Group Leader, IBM R&D Lab