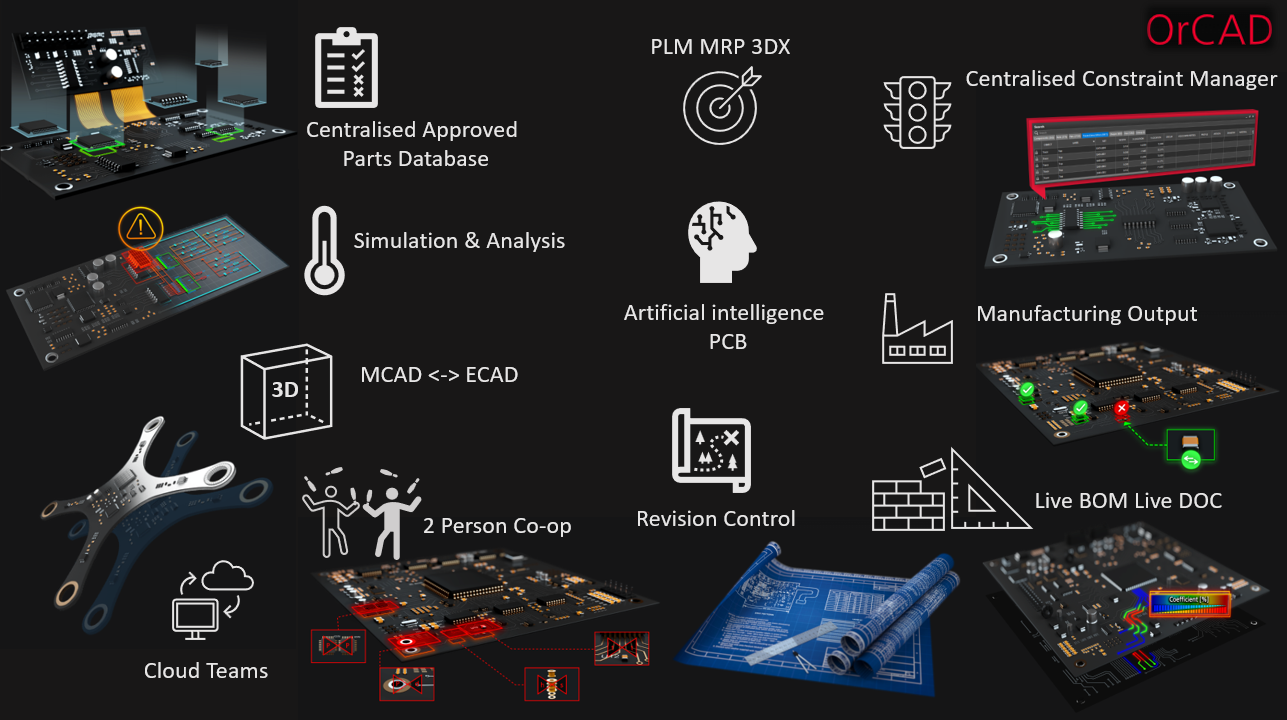

OrCAD X and Allegro X PCB Matrix Key: A tick confirms that the feature is included in the suite. An option name means you need to purchase the option to get the feature included in the suite

1:02 Circuit Replicate - Design Reuse OrCAD X

2:28 Via Arrays OrCAD X

3:24 New User Interface OrCAD X

7:02 Design Review Markup OrCAD X

10:20 Super Fast 3D engine OrCAD X

12:35 3D Flexi OrCAD X

15:10 3D DRC Design Rule Check OrCAD X

17:24 Dynamic Shapes OrCAD X

20:10 Live Doc OrCAD X

24:48 X AI Artificial intelligence OrCAD X

26:38 DRC Browsing OrCAD X

28:40 Export to Manufacturing OrCAD X

Please also view the PDF Presentation on what is new in OrCAD X and Allegro X here