The new, easy-to-use Design For Test (DFT) software will help you find and fix common design errors at an early stage. Because physical access to pins under many IC packages such as BGAs is virtually impossible, it is critical to ensure the testability of these devices via JTAG. Failure to do so could lead to a board re-spin and a costly project delay.

XJTAG DFT Assistant helps you to validate correct JTAG chain connectivity, through full integration with OrCAD Capture.

• Freely available to OrCAD Capture users (version 17.2 and above)

• Catch errors in the JTAG chain(s) before producing any hardware

• Harness the full power of boundary scan to improve testability

This feature identifies common errors in a JTAG scan chain, such as incorrectly connected and terminated Test Access Port (TAP) signals. A single connection error could prevent an entire scan chain from working. XJTAG Chain Checker finds and reports connectivity issues during schematic capture so you can correct these before assembly and avoid board re-spins.

Visualize the extent of boundary scan access overlaid onto your schematic diagram and instantly see which components are accessible for JTAG testing - and which are not. Using this insight you can extend test coverage even further, making your boards easier to test and, resulting in faster time to manufacturing and to market.

Visit www.telexsus.com to find more

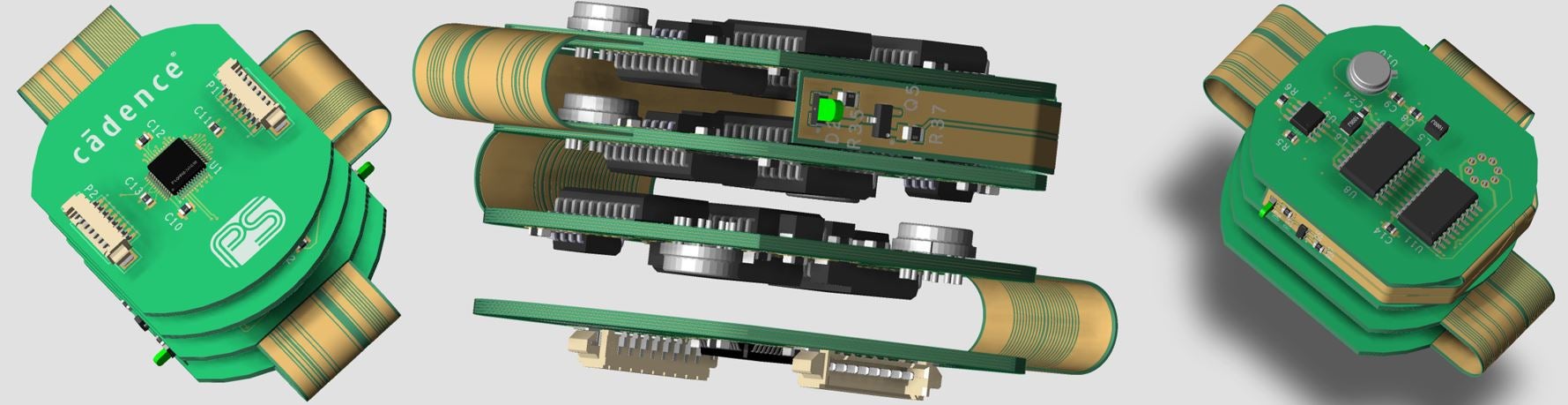

Parallel Systems, providing world leading EDA software, sales, support and training since 1997